An Integrated Framework for Aging Analysis Based on an Age-Aware Cell Library

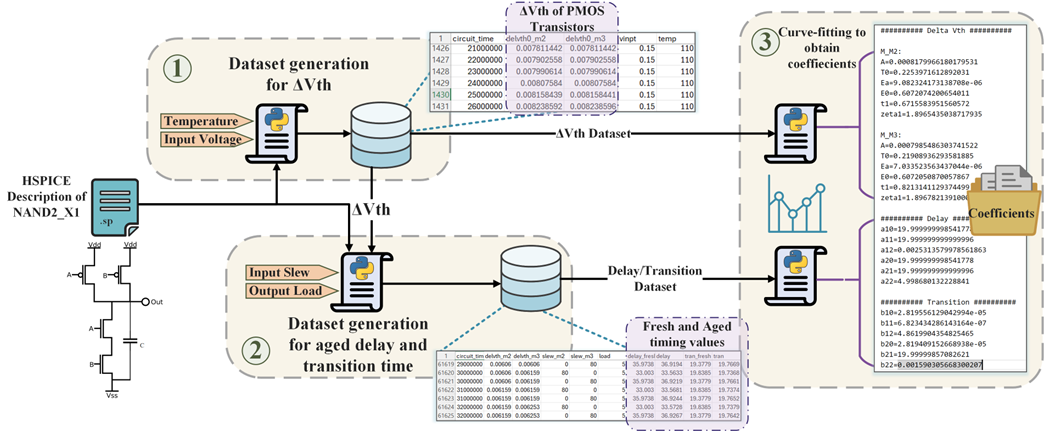

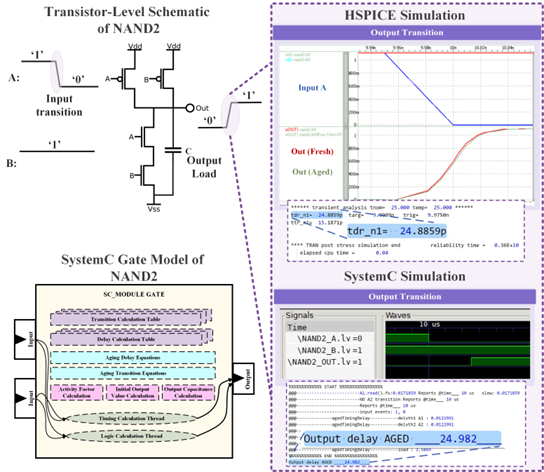

Designers are often compelled to make compromises to ensure reliable functionality as transistors age, which can hinder efficiency. To address this, using age-aware Design Space Exploration (DSE) can improve design efficiency without sacrificing performance. Conventional aging analysis tools are slow and impractical for complex circuits. Thus, this study introduces a gate-level back-annotation of aging characteristics that improves simulation efficiency and retains accuracy at an acceptable level. This method is used in a uniform framework that brings in aging considerations in an event-based simulation environment, and automates extraction of required information to fit in the mentioned environment. This results in calibration of simulation units that are defined as gate models for bridging device-level to system-level analysis. Considering the today’s digital design complexities, this work incorporates the conventional aging analysis into an event-based simulator which provides much faster analysis time. This approach achieves an average speedup of 7.12 versus HSPICE and maintains accuracy with an average pessimism of 0.29%, making it a practical environment for analyzing aging effects on reliability.

This work is accepted for IEEE ETS 2025 conference.

Authors list: Amirmahdi Joudi, Negin Safari, Fatemeh Mohammadzadeh, Katayoon Basharkhah, Fatemeh Sheikhshoaei, Zainalabedin Navabi