A Configurable Hardware Accelerator for Brain-Computer Interface Applications

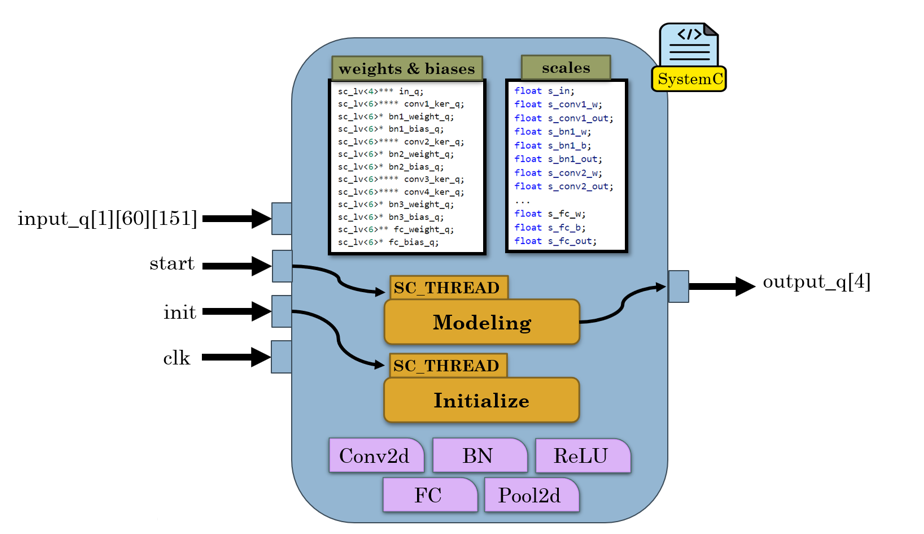

For my Master’s thesis project, I am focusing on analyzing various deep neural networks utilized in motor imagery applications within brain-computer interfaces. Presently, I have chosen to develop a flexible hardware implementation for EEG-Net, a convolutional neural network. In the initial phase of this project, I am creating a system-level model of the network using SystemC. This high-level description allows us to control the bit-width of the operations within the accelerator and do DSE. This approach allows us to evaluate the functionality of the accelerator in conjunction with other components of a System on Chip (SoC), facilitating design space exploration. The subsequent phase involves proposing a detailed hardware architecture and generating its layout. The ultimate objective is to incorporate power optimization techniques to ensure the hardware is suitable for implantable devices. The current dataset that is being tested is BCI-IV2a competition.

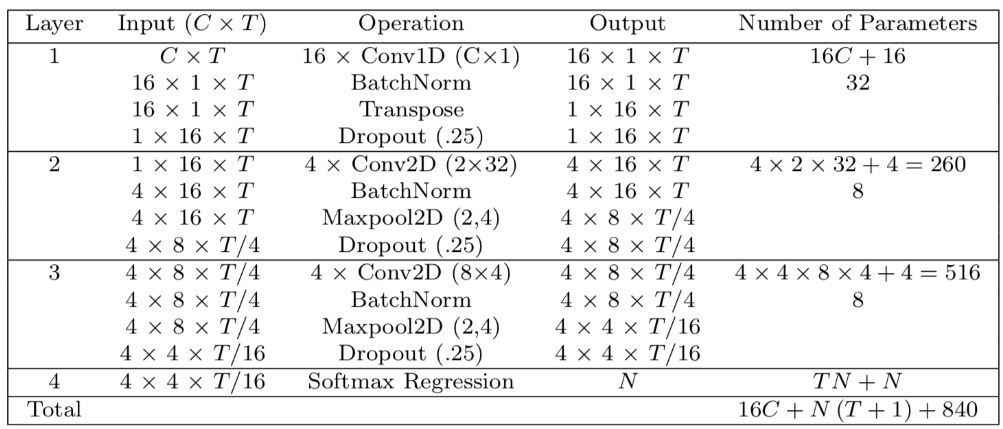

Here is the general description of EEG-Net layers, which is taken from its main paper:

Here is the block diagram of the SystemC description: